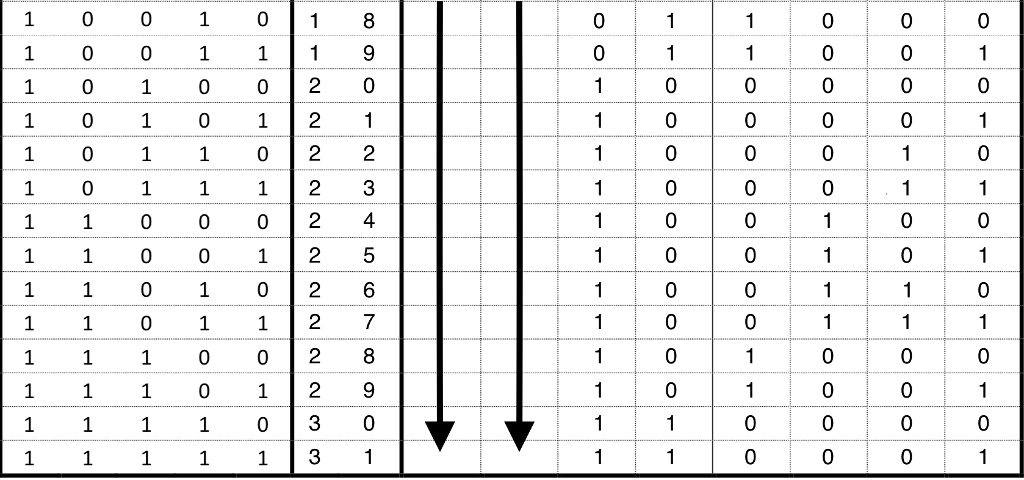

Since the maximum value each 4-bit BCD digit can have is 9, the component needs to make an adjustment if the doubling process results in a number greater than 9. Once the entire number is shifted in, the new BCD number is equivalent to the original binary one.

With each shift, it doubles the register’s current value and adds the new bit. This component completes the same process to perform a Binary to BCD conversion. Once you have shifted in all of the bits, the new register contains the original number. Each time you shift in a bit, you are doubling the current number in the register and adding the new bit. Suppose you shift a number from one binary register into another binary register, one bit at a time. The concept behind this Binary to BCD converter is to shift the number from one shift register into another shift register, most significant bit (MSB) first. Example Implementation Theory of Operation An example design that uses this Binary to BCD Converter to make a Multiple Digit 7-Segment Display Driver is available here.įigure 1. Figure 1 illustrates a typical example of the Binary to BCD converter integrated into a system. Resource requirements depend on the implementation. It was designed using Quartus II, version 13.1.0. The component reads in a binary number from user logic over a parallel interface and outputs the BCD equivalent. This details a Binary to BCD converter circuit, written in VHDL for use in CPLDs and FPGAs. Configurable number of BCD output digits.Configurable size of binary input number.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed